Fig. 1C

Fig.10

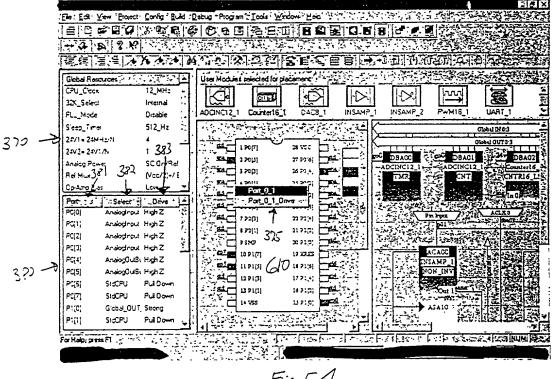

Fig.5A

Fig.5C

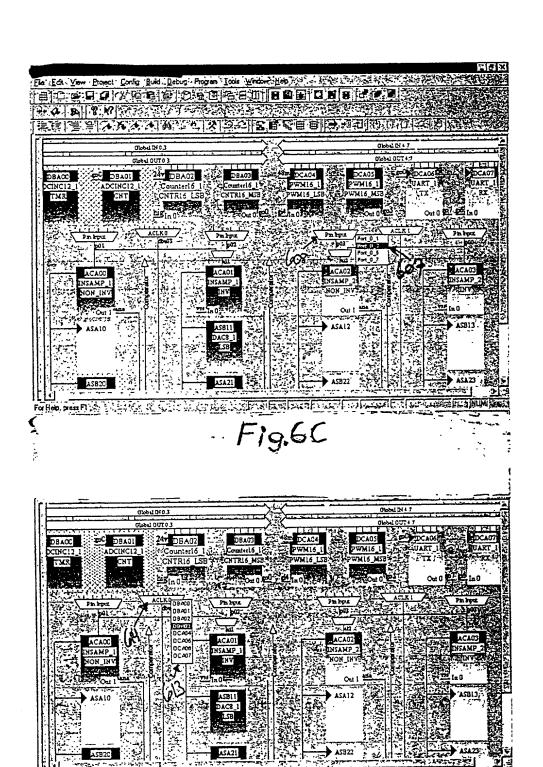

For Heio, press F15

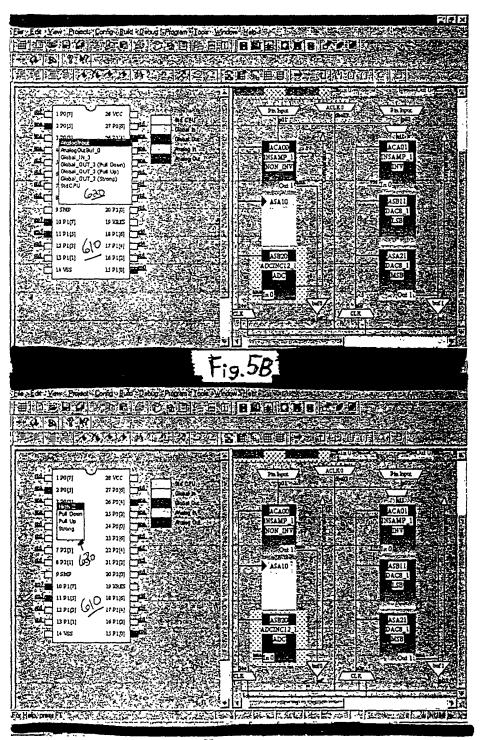

Fig.6D

```

configtbl asm

: Personalization tables

export LoadConfigTBL_project_Bank1

export LoadConfigTBL_project_Bank0

LoadConfigTBL_project_Bank1

; Global Register values

61h, 03h

. AnalogClockSe'ect register

ರಶ

¢٥

60h, 08h

; AnalogColumnClockSelect register

ರರ

62h, 30h

, AnalogIOControl register

co

63h, 00h

; AnalogModulatorControl register

دی

e1h, 30h

; OscillatorControl_1 register

đ٥

00n, 00n

; Port_0_DriveMade_0 register

ರರಿ

01h, 3fh

; Port_0_DriveMode_1 register

; Port_1_DriveMode_0 register

ď٥

04h, a1h

ď٥

05h, 50h

; Part_1_DriveMode_1 register

ರರ

08h, 00h

; Port_2_OnveMode_0 register

09n, 00n

, Port_2_DriveMode_1 register

0ch, 00h

; Port_3_DriveMode_0 register

đb

đБ

0dh, 00h

; Port_3_DriveMode_1 register

¢b

10h, 00h

; Part_4_DriveMode_0 register

ಧರಿ

11h, 00h

; Port_4_DriveMode_1 register

đ٥

14h, 00h

: Port 5_DriveMode_0 register

ರಶ

15h, 00h

; Port_5_DriveMode_1 register

ďþ

e3h, 84h

; VoltageMonitorControl register

. Instance name ADCINC12_1, User Module ADCINC12

Instance name ADCINC12_1, Block Name ADC(ASB20)

90h, 90h

;ADCINC12_1_AloDcr0

ď۵

91n, 60n

;ADCINC12_1_AtoDcr1

92h, 60h

;ADCINC12_1_AtoDcr2

đb

93h, f0h

;ADCINC12_1_AtoDcr3

Instance name ADCINC12_1, Block Name CNT(DBA01)

:ADCINC12_1_CounterFN

24n, 21n

25h, 48h

;ADCINC12_1_CounterSL

ďÞ

ďb

26h, 00h

;AOCINC12_1_CounterOS

TMR(DBA00)

Instance name ADGING12_1, Block Name

20h, 20h

;ADCINC12_1_TimerFN

21h, 18h

:ADCINC12_1_TimerSL

¢b

;ADCINC12_1_TimerOS

ďÞ

22h, 00h

, Instance name Counter16_1, User Module Counter16

Instance name Counter16_1, Block Name CNTR16_LSB(DBA02)

;Counter16_1_FUNC_LS8_REG

ďþ

28h, 01h

29h, 16h

;Counter16_1_INPUT_LS8_REG

ರರಿ

dъ

2ah, 00h

:Counter16_1_OUTPUT_LS8_REG

Instance name Counter16_1, Block Name CNTR16_MS8(DBA03)

2ch, 21h

:Counter16_1_FUNC_MSB_REG

ďЪ

;Counter16_1_INPUT_MSB_REG

2dh, 36h

đb

;Counter16_1_OUTPUT_MS8_REG

db

2eh, 04h

, Instance name DAC8_1, User Module DAC8

Instance name DAC8_1, Block Name LS8(ASB11)

:DAC8_1_LS8_CR0

ďÞ

84h, 80h

;DAC8_1_LSB_CR1

đb

85h, 80h

DAC8_1_LSB_CR2

đъ

86h, 20h

ďb

87h, 30h

;DAC8_1_LS8_CR3

instance name DAC8_1, Block Name MS8(ASA21)

94h, a0h

;DAC8_1_MSB_CR0

```

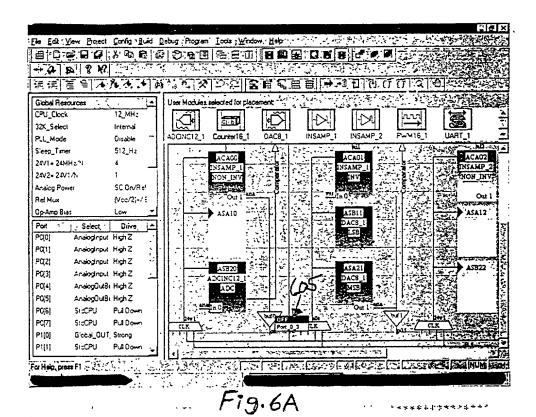

Fig. 7A

## (Continued)

```

ďδ

95h, 41h

.DAC8_1_MSB_CR1

ďЪ

96n, a0h

:DAC8_1_MSB_CR2

đ٥

97h, 30h

,DAC8_1_MSB_CR3

; Instance name INSAMP_1, User Module INSAMP

Instance name INSAMP_1, Block Name INV(ACA01)

INSAMP_1_INV_CRO

фb

75h, beh

.INSAMP_1_INV_CR1

ďb

76h, 21h

77h, 20h

;INSAMP_1_INV_CR2

đЪ

Instance name INSAMP_1, Block Name NON_INV(ACA00)

;INSAMP_1_NON_INV_CRO

ďЪ

71h, 3ch

đb

72h, a1h

;INSAMP_1_NON_INV_CR1

ďb

73h, 20h

;INSAMP_1_NON_INV_CR2

; Instance name INSAMP_2, User Module INSAMP

Instance name INSAMP_2, Block Name INV(ACA03)

ďb

7dh, ceh

,INSAMP_2_INV_CRO

dЬ

7eh, 21h

:INSAMP_2_INV_CR1

ďb

7fh, 20h

;INSAMP_2_INV_CR2

Instance name INSAMP_2, Block Name NON_INV(ACA02)

đb

79h, 2ch

:INSAMP_2_NON_INV_CR0

ďδ

7ah, a1h

;INSAMP_2_NON_INV_CR1

7bh, 20h

:INSAMP_2_NON_INV_CR2

; Instance name PWM16_1, User Module PWM16

Instance name PWM16_1, Block Name PWM16_LSB(DCA04)

30h, 01h

:PWM16_1_FUNC_LSB_REG

:PWM16_1_INPUT_LS8_REG

32h, 00h

;PWM16_1_OUTPUT_LSB_REG

đb

Instance name PWM16_1, Block Name PWM16_MS8(DCA05)

:PWM16_1_FUNC_MSB_REG

dЪ

34h, 21h

;PWM16_1_INPUT_MS8_REG

đЪ

35h, 34h

:PWM16_1_OUTPUT_MSB_REG

ďЪ

36h, 05h

; Instance name UART_1, User Module UART

Instance name UART_1, Block Name RX(DCA07)

;UART_1_RX_FUNC_REG

3ch, 05h

đb

:UART_1_RX_INPUT_REG

3dh, eth

ďĎ

3eh, 00h

:UART_1_RX_OUTPUT_REG

ďΦ

Instance name UART_1, Block Name TX(DCA06)

;UART_1_TX_FUNC_REG

ďb

38h, 0dh

;UART_1_TX_INPUT_REG

39h, 0th

dh

;UART_1_TX_OUTPUT_REG

ďδ

3ah, 07h

ďЪ

LoadConfigTBL_project_Bank0.

; Global Register values

đb

; AnalogColumnInputSelect register

ďЪ

63h, 05h

; AnalogReferenceControl register

đb

65h, 00h

; AnalogSyncControl register

ďb

e6h. 00h

; DecimatorControl register

02h, 00h

; Port_0_Bypass register

db

db

06h, fth

: Port_1_Bypass register

; Port_2_Bypass register

đb

0ah, 00h

dЬ

0eh, 00h

; Port_3_Sypass register

12h, 00h

: Port_4_Bypass register

đb

16h, 00h

; Port_5_Bypass register

; Instance name ADCINC12_1, User Module ADCINC12

Instance name ADCINC12_1, Block Name ADC(ASS20)

Instance name ADCINC12_1, Block Name CNT(DBA01)

```

Fig. 7B

# (Continued)

| db                   | 27h, COh               | ;ADCINC12_1_CounterCR0       |

|----------------------|------------------------|------------------------------|

| db                   | 25h, 00h               | ;ADCINC12_1_CounterDR1       |

| ₫Þ                   | 26h, 00h               | ;ADCINC12_1_CounterDR2       |

| . Instance name At   | OCINC12_1, Block Nam   | ne TMR(DBA00)                |

| db                   | 23h, 00h               | :ADCINC12_1_TimerCR0         |

| dc                   | 21h, 00h               | ;ADCINC12_1_TimerDR1         |

| cb                   | 22h, 00h               | ,ADCINC12_1_TimerDR2         |

| , Instance name Coun | ler16_1, User Module ( | Counter16                    |

| . Instance name Co   | ounter16_1, Block Nam  | e CNTR16_LSB(DBA02)          |

| ರರಿ                  | 2ph, 00h               | ,Counter16_1_CONTAOL_LSB_REG |

| db                   | 29h, 80h               | ;Counter16_1_PERIOD_LS8_REG  |

| db                   | 2ah, 64h               | ,Counter16_1_COMPARE_LS8_REG |

| , Instance name Co   | ounter16_1, Block Nam  | e CNTR16_MS8(DBA03)          |

| db                   | 2fh, 00h               | :Counter16_1_CONTROL_MSB_REG |

| db                   | 2dh, 00h               | ;Counter16_1_PERIOD_MSB_REG  |

| db                   | 2eh, 00h               | ;Counter16_1_COMPARE_MSB_RE0 |

| , Instance name DACS | 3_1, User Module DAC   | 8                            |

| ; Instance name D    | AC8_1, Block Name LS   | (B(ASB11)                    |

| , Instance name Di   | AC8_1, Block Name MS   | SB(ASA21)                    |

| , Instance name INSA | MP_1, User Module (N   | SAMP                         |

| , Instance name IN   | SAMP_1, Block Name     | INV(ACA01)                   |

| , Instance name IN   | SAMP_1, Block Name     | NON_INV(ACA00)               |

| , instance name INSA | MP_2. User Module IN   | SAMP                         |

| , Instance name IN   | SAMP_2, Block Name     | INV(ACA03)                   |

| . Instance name IN   | SAMP_2, Block Name     | NON_INV(ACA02)               |

| , Instance name PWM  | I16_1, User Module PV  | VM16                         |

| , Instance name Pt   | WM16_1, Block Name I   | PWM16_LSB(DCA04)             |

| ďb                   | 33n, 00n               | :PWM16_1_CONTROL_LSB_REG     |

| ďb                   | 31h, 37h               | ;PWM16_1_PERIOD_LS8_REG      |

| db                   | 32h, 64h               | :PWM16_1_PWDITH_LS8_REG      |

| ; Instance name Pt   | WM16_1, Block Name     | PWM16_MSB(DCA05)             |

| db                   | 37h, 00h               | ;PWM16_1_CONTROL_MS8_REG     |

| ďð                   | 35h, 00h               | ;PWM16_1_PERIOD_MSB_REG      |

| db                   | 36h, 00h               | ;PWM16_1_PWDITH_MSG_REG      |

| , Instance name UAR  | T_1, User Module UAR   | r                            |

| ; Instance name U    | ART_1, Block Name R    | X(DCA07)                     |

| ďЪ                   | 3fh, 00h               | :UART_1_RX_CONTROL_REG       |

| db                   | 3dh, 00h               | ;UART_1_                     |

| ďb                   | 3eh, 00h               | ;UART_1_RX_BUFFER_REG        |

| , instance name U    | ART_1, Block Name TX   | K(DCA06)                     |

| db                   | 3bh, 00h               | :UART_1_TX_CONTROL_REG       |

| db                   | 39h, 00h               | ;UART_1_TX_BUFFER_REG        |

| ďb                   | 3ah, 00h               | ;UART_1_                     |

| db                   | ffh                    |                              |

|                      |                        |                              |

, PSoC Configuration file trailer PsocConfig.asm

```

; PSoCConfig.asm

; This file is generated by the Device Editor on Application Generation.

; It contains code which loads the configuration data table generated in

; the file PSoCConfigTBL.asm

export LoadConfigInit

export _LoadConfigInit

export LoadConfig_project

export _LoadConfig_project

FLAG_CFG_MASK:

equ

10h

;M8C flag register REG address bit

mask

END_CONFIG_TABLE: equ

tth

;end of config table indicator

_LoadConfigInit:

LoadConfigInit:

LoadConfig_project

ret

; Load Configuration project

_LoadConfig_project:

LoadConfig_project:

F, FLAG_CFG_MASK

;set for

bank 1

mov

A, >LoadConfigTBL_project_Bank1 ;load bank 1 table

X. <LoadConfigTBL_project_Bank1

mov

LoadConfig

call

:load the

bank 1 values

F,-FLAG_CFG_MASK

;switch

and

to bank 0

A, >LoadConfigT8L_project_Bank0 ;load bank 0 table

mov

X, <LoadConfigTBL_project_Bank0

mov

call

LoadConfig

;load the

bank 0 values

; LoadConfig

; This function is not exported. It assumes that the address of the table

; to be loaded is contained in the X and A registers as if a romx instruction

```

Fig. 8A

#### (continued)

; is the next instruction to be executed, i.e. lower address in  $\boldsymbol{X}$  and uppper

; address in A. There is no return value.

```

LoadConfig

LoadConfigLp.

;save config table address on stack

push

Х

push

romx

;load config address

A, END_CONFIG_TABLE

;check for end of table

стр

;if so, end of load

EndLoadConfig

ĵΖ

;save the address away

X, SP

mov

mov

[X], A

retrieve the table address

рор

х

pop

;advance to the data byte

ICC

NoOverFlow1

check for overflow

Jnc

;if so, increment MSB

ınç

NoOverFlow1:

;save the config table address

push

again

push

;load the config data

romx

retrieve the config address

X, SP

X, [X]

mov

;write the config data

reg[X], A

;retrieve the table address

Α

рор

рор

X

;advance to the next

х

inc

address

NoOverFlow2

;check for overflow

jnc

;if so, increment MSB

înc

Α

NoOverFlow2:

LoadConfigLp

;loop back

lmb

EndLeadConfig:

;clean up the stack

рор

Α

Α

рор

ret

```

Fig. 8B

|                                                 | mov reg[ADCINC12_1_AtoDcr3],A                      |  |

|-------------------------------------------------|----------------------------------------------------|--|

|                                                 | ret                                                |  |

| ;; ADCINC12.asm                                 |                                                    |  |

|                                                 |                                                    |  |

| : Assembler source for the 12 bit Incremential  | ;; Stop:                                           |  |

| :A/D converter.                                 | :: SetPower:                                       |  |

|                                                 | :: Removes power from the module's analog          |  |

|                                                 | ;;PSoc block.                                      |  |

| 14<br>                                          | :: INPUTS: None.                                   |  |

| 10                                              | :: OUTPUTS: None.                                  |  |

| export ADCINC12_1_Start                         | <u></u>                                            |  |

| export_ADCINC12_1_Start                         | ADCINC12_1_Stop:                                   |  |

| export_ADCINC12_1_SetPower                      | _ADCINC12_1_Stop                                   |  |

| export_ADCINC12_1_SetPower                      | and reg[ADCINC12_1_AtoDcr3], -03h                  |  |

| export_ADCING12_1_Stop                          | ret                                                |  |

| export_ADCINC12_1_Stop                          |                                                    |  |

| export_ADCINC12_1_GetSamples                    |                                                    |  |

| export_ADCINC12_1_GetSamples                    | ;; Get_Samples:                                    |  |

| export_ADCINC12_1_StopAD                        | :: SetPower:                                       |  |

| export_ADCINC12_1_StopAD                        | :: Starts the A/D convertor and will place data is |  |

| export ADCINC12_1_fisData                       | ;;memory. A flag                                   |  |

| export_ADCINC12_1_flsData                       | : is set whenever a new data value is available.   |  |

| export ADCINC12_1_iGetData                      | :: INPUTS: A passes the number of samples (0       |  |

| export _ADCINC12_1_iGetData                     | ;;is continous).                                   |  |

| export ADCINC12_1_ClearFlag                     | :: OUTPUTS: None.                                  |  |

| export _ADCINC12_1_ClearFlag                    |                                                    |  |

| 5,port_7,000,0012,00000000000000000000000000000 | ADCINC12_1_GetSamples:                             |  |

| include "ADCINC12_1.inc"                        | _ADCINC12_1_GetSamples:                            |  |

| include "m8c.inc"                               | mov (ADCINC12_1_bincrC],A ;number                  |  |

|                                                 | of samples                                         |  |

| LowByte: equ 1                                  | or reg[INT_MSK1],(ADCINC12_1_TimerMask             |  |

| HighByte: equ 0                                 | ADCINC12_1_CounterMask)                            |  |

|                                                 | :Enable both interrupts                            |  |

|                                                 | mov [ADCINC12_1_cTimerU],0 ;Force the              |  |

| ***************************************         | :Timer to do one cycle of rest                     |  |

| :: Start:                                       | or reg[ADCINC12_1_AtoDcr3],10h ;force the          |  |

| :: SetPower:                                    | ;Integrator into reset                             |  |

| : Applies power setting to the module's analog  | mov [ADCINC12_1_cCounterU],ffh ;Initialize         |  |

| ::PSoc block.                                   | ;Counter                                           |  |

| :: INPUTS: A contians the power setting         |                                                    |  |

| :: OUTPUTS: None.                               | mov reg[ADCINC12_1_TimerDR1],ffh                   |  |

|                                                 | mov reg[ADCINC12_1_CounterDR1],ffh                 |  |

| ADCINC12_1_Start:                               | mov reg[ADCINC12_1_TimerCR0],01h ;enable           |  |

| _ADCINC12_1_Start:                              | ;the Timer                                         |  |

| ADCINC12_1_SetPower:                            | mov [ADCINC12_1_fincr],00h ;A/D Data               |  |

| _ADCINC12_1_SetPower:                           | ;Ready Flag is reset                               |  |

| and A,03h                                       | ret                                                |  |

| or A,f0h                                        |                                                    |  |

### (Continued)

\_ADCINC12\_1\_iGetData mov X,[(ADCINC12\_1\_iInc + righByte)] mov A.[(ADCINC12\_1\_ilncr + LowByte)] ;; Completely shuts down the A/D is an orderly ;;manner, Both the ;; Timer and COunter interrupts are disabled. ;; INPUTS. None. ;; OUTPUTS None. ;; ClearFlag: :: clears the data ready flag ;; INPUTS: None. ADCINC12\_1\_StopAD. \_ADCINC12\_1\_StopAD: ;; OUTPUTS: None. mov reg(ADCINC12\_1\_TimerCR0),00h ADCINC12\_1\_ClearFlag: disable the Timer mov reg[ADCINC12\_1\_CounterCR0],00h \_ADCINC12\_1\_ClearFlag ;disable the Counter mov [ADCINC12\_1\_fincr],00h nop nop ADCINC12\_1\_API\_End and reg[INT\_MSK1],-(ADCINC12\_1\_TimerMask1 ADCINC12\_1\_CounterMask) :Disable both ;;interrupts or reg[ADCINC12\_1\_AtoDcr3],10h ;reset ;;integrator ret ;; flsData: ;, Returns the status of the A/D Data ;; is set whenever a new data value is available. ;; INPUTS: None. .: OUTPUTS: A returned data status A =: 0 no ::data available !=: 0 data available ADCINC12\_1\_flsData: \_ADCINC12\_1\_flsData: mov A,[ADCINC12\_1\_fincr] ;; iGetData: ;; Returns the data from the A/D. Does not ;;check if data is ;; available. ;; is set whenever a new data value is available. ;; INPUTS: None. ;; OUTPUTS: X:A returns the A/D data value. ADCINC12\_1\_iGetData:

F. 9B

```

// ADCINC12_1.h for the 12 bit incremental A/D converter

//

// C declarations for the ACDINC12 User Module.

//

#define ADCINC12_1_OFF

0

#define ADCINC12_1_LOWPOWER 1

#define ADCINC12_1_MEDPOWER 2

#define ADCINC12_1_HIGHPOWER 3

#pragma fastcall ADCINC12_1_Start

#pragma fastcall ADCINC12_1_SetPower

#pragma fastcall ADCINC12_1_GetSamples

#pragma fastcall ADCINC12_1_StopAD

#pragma fastcall ADCINC12_1_Stop

#pragma fastcall ADCINC12_1_flsData

#pragma fastcall ADCINC12_1_iGetData

#pragma fastcall ADCINC12_1_ClearFlag

extern void ADCINC12_1_Start(char power);

extern void ADCINC12_1_SetPower(char power);

extern void ADCINC12_1_GetSamples(char chout);

extern void ADCINC12_1_StopAD(void);

extern void ADCINC12_1_Stop(void);

extern char ADCINC12_1_flsData(void);

extern int ADCINC12_1_iGetData(void);

extern void ADCINC12_1_ClearFlag(void);

```

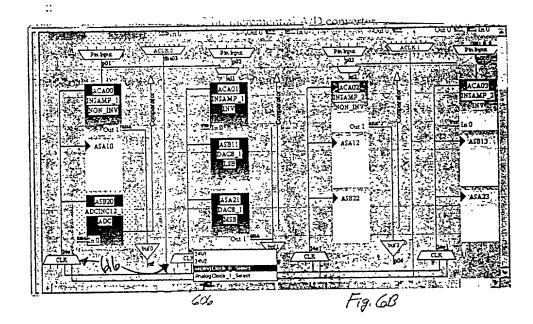

Fig. 10

```

;; ADCINC12_1.inc for the 12 bit incremental A/D converter

;; Assembler declarations for the ACDINC12 User Module.

90h

ADCINC12_1_AtoDcr0: equ

ADCINC12_1_AtoDcr1:

91h

ADCINC12_1_AtoDcr2:

92h

equ

93h

ADCINC12_1_AtoDor3:

equ

ADCINC12_1_CounterFN: equ

ADCINC12_1_CounterSL: equ

25h

26h

ADCINC12_1_CounterOS:equ

ADCINC12_1_CounterDR0:

24h

equ

ADCINC12_1_CounterDR1:

equ

25h

ADCINC12_1_CounterDR2:

26h

equ

27h

ADCINC12_1_CounterCR0:

equ

20h

ADCINC12_1_TimerFN: equ

ADCINC12_1_TimerSL: equ

ADCINC12_1_TimerOS: equ

ADCINC12_1_TimerDR0: equ

ADCINC12_1_TimerDR1: equ

ADCINC12_1_TimerDR2: equ

ADCINC12_1_TimerCR0: equ 23h

ADCINC12_1_TimerMask: equ 01h

ADCINC12_1_CounterMask: equ 02h

ADCINC12_1_OFF:

equ 0

ADCINC12_1_LOWPOWER: equ 1

ADCINC12_1_MEDPOWER: equ 2

ADCINC12_1_HIGHPOWER: equ 3

ADCINC12_1_NUMBITS: equ 12

```

Fig. 11

```

g------

.. ADCINC12int asm

.: Assembler source for interrupt routines the 12 bit incremential

export ACCINC12_1_CNT_INT

export ADCINC12_1_TMR_INT

include "ADCINC12_1 inc"

include "m8c inc"

area bss(RAM)

ADCINC12_1_cTimerU BLK 1 :The Upper byte of the Timer

ADCINC12_1_cCounterU BLK 1 :The Upper byte of the Counter

_ADCINC12_1_ilner

ADCINC12_1_lincr BLK 2 A/O value _AOCINC12_1_lincr AOCINC12_1_lincr BLK 1 :Data Valid Flag

ADCINC12_1_blncrC: BLK 1 ;# of times to run A/D

area text(ROM,REL)

export ADCINC12_1_cTimerU

export ADCINC12_1_cCounterU

export_ADCINC12_1_ilner

export ADCINC12_1_ilner

export _ADCINC12_1_finct

export ADCINC12_1_fincr

export ADCINC12_1_bincrC

LowByte. equ 1

HighByte equ 0

: CNT_INT

... Decrement the upper (software) half on the counter whenever the

.: lower (hardware) half of the counter underflows.

;; INPUTS. None

:: OUTPUTS None.

ADCINC12_1_CNT_INT.

dec [ADCINC12_1_cCounterU]

. TMR_INT.

.: This routine allows the counter to collect data for 64 timer cycles

.. This routine then holds the integrator in reset for one cycle while

## the A/D value is calculated.

## INPUTS None.

;; OUTPUTS: Nane.

ADCING12_1_TMR_INT:

dec [ADCING12_1_eTimerU]

, if(upper count >=0)

ic else1

reti

else1 ((upper count decremented pass 0)

tst reg[ADCINC12_1_AtoDcr3],10h ,to change when ice is fixed dbz

```

Fig 12A

#### (continued)

```

. If(AD has been in reset mode)

mov reg[ADCINC12_1_CounterCR0],01h , Enable Counter

and reg(ADCINC12_1_AtoDcr3],=10h ; Enable Analog Integrator mov [ADCINC12_1_cTimerU] ((1<<(ADCINC12_1_NUMBITS + 6))-1)

. This will be the real counter value

(abom etargathi ni nead aart CVA), Saala

mov reg[ADCINC12_1_CounterCR0],00h _disable counter

or Forn

Enable the interrupts

Good place to add code to switch inputs for multiplexed input to ADC

or reg(ADCINC12_1_AroDor3), 10h ,Reset Integrator

mov [(ADCINC12_1_ilncr + LowByte)],fth

mov [(ADCINC12_1_ilncr + HighByte)],(fth - (1<<(ADCINC12_1_NUMBITS - 7)))

mov A, reg[ADCINC12_1_CounterDR0] ,read Counter

mov A, reg[ADCINC12_1_CounterDR2] ,now you really read the data

sub [(ADCINC12_1_sincr + LowByte)],A

mov A.[ADCINC12_1_cCounterU]

sco [(ADCINC12_1_incr + HighByte)],A

рор А

cmp [(ADCINC12_1_ilincr + HighByte)],(1<<(ADCINC12_1_NUMBITS - 7))

jnz endif10

if(max positive value)

dec [(ADCINC12_1_ilner + HighByte)]

mov ((ADCINC12_1_ilner + LowByte)].ffh

endif10:

asr ((AOCINC12_1_ilncr + HighByte))

; divide by 4

rrc ((ADCINC12_1_incr + LowByte))

asr [(ADCINC12_1_ilncr + HighByte)]

ms [(ADCINC12_1_ilner + LowByte)]

may [AOCINC12_1_finer].01h

:Set AD data flag

. User code here for interrupt system.

cmp [ADCINC12_1_bincrC],00h

if(ADCINC12_1_bincrC is not zero)

dec [ADCINC12_1_bincrC]

jaz endil4

if(ADCINC12_1_bincrC has decremented down to zero to 0)

mov reg(ADCINC12_1_TimerCR0),00h ,disable the Timer mov reg(ADCINC12_1_CounterCR0),00h ;disable the Counter

пор

and reg[INT_MSK1],-(ADCINC12_1_TimerMask I ADCINC12_1_CounterMask)

or reg(ADCINC12_1_AtoDcr3],10h

,Reset Integrator

reti

endif4.;

endi3:

end:f2::

mov [ACCINC12_1_cTimerU],00h __

,Set Timer for one cycle of reset

mov [ADCINC12_1_cCounterU], Ifh

,Set Counter hardware for easy enable

mov reg(ADCINC12_1_CounterOR1],ffh

reti

erdit;

```

ADCINC12\_1\_APIINT\_END: A/D converter

Fig. 12. B

| 1300                                              |                                             |

|---------------------------------------------------|---------------------------------------------|

| ; Interrupt Vector Table                          | org 1Ch ; PSoC Block DCA0 ;Interrupt Vector |

| *****************************                     | ljmp PWM16_1INT                             |

| ;                                                 | reti                                        |

| ; Interrupt vector table entries are 4 bytes long |                                             |

| ;and contain the code                             | org 20h ; PSoC Block DCA06                  |

| ; that services the interrupt (or causes it to be | ;Interrupt Vector                           |

| ;serviced)                                        | Ijmp UART_1TX_INT                           |

| ;                                                 | reti                                        |

| •                                                 | org 24h ; PSoC Block DCA07                  |

|                                                   | ;Interrupt Vector                           |

| AREA TOP(ROM, ABS)                                | ljmp UART_1RX_INT                           |

|                                                   | /305 reti                                   |

| org 0 ; Reset Interrupt Vector                    |                                             |

| jmp _start : First instruction                    | org 28h ; Analog Column 0                   |

| executed following a Reset                        | ;Interrupt Vector                           |

| 0                                                 | // call void_handler                        |

| org 04h ; Supply Monitor Interrupt ; Vector       | reti                                        |

| // call_void_handler                              | org 2Ch ; Analog Column 1                   |

| reti                                              | ;Interrupt Vector                           |

| 7011                                              | // call_void_handler                        |

| org 08h ; PSoC Block DBA00                        | reti                                        |

| Interrupt Vector                                  |                                             |

| Bus- Ijmp ADCINC12_1_TMR_INT                      | org 30h ; Analog Column 2                   |

| reti                                              | ;Interrupt Vector                           |

|                                                   | // call void_handler                        |

| org 0Ch ; PSoC Block DBA01                        | reti                                        |

| ;Interrupt Vector                                 |                                             |

| /305 Jimp ADCINC12_1_CNT_INT                      | org 34h ; Analog Column 3                   |

| reti                                              | ;Interrupt Vector // call_void_handler      |

| org 10h ; PSoC Block DBA02                        | reti                                        |

| ;Interrupt Vector                                 | 16.1                                        |

| // call_void_handler                              | org 38h ; GPIO Interrupt Vector             |

| reti                                              | // call_void_handler                        |

|                                                   | reti                                        |

| org 14h ; PSoC Block DBA03                        |                                             |

| ;Interrupt Vector                                 | org 3Ch ; Sleep Timer Interrupt             |

| ljmp Counter16_1INT                               | ;Vector                                     |

| reti                                              | jmp SleepTimerISR<br>reti                   |

| org 18h ; PSoC Block DCA04                        | 100                                         |

| ;Interrupt Vector                                 |                                             |

| // call void_handler                              |                                             |

| reti                                              |                                             |

Fig. 13A

| 1350                   | 1352                      | 1353       |

|------------------------|---------------------------|------------|

| 1351                   | /                         |            |

| bootasm Interrupt Name | Data Sheet Interrupt Name | Type       |

| start                  | Reset                     | Fixed      |

| Interrupt1             | Supply Monitor            | Fixed      |

| Interrupt2             | DBA00                     | PSoC Block |

| Interrupt3             | DBA01                     | PSoC Block |

| Interrupt4             | DBA02                     | PSoC Block |

| Interrupt5             | D8A03                     | PSoC Block |

| Interrupt6             | DCA04                     | PSoC Block |

| Interrupt7             | DCA05                     | PSoC Block |

| Interrupt8             | DCA06                     | PSoC Block |

| Interrupt9             | DCA07                     | PSoC Block |

| Interrupt10            | Analog Column 0           | PSoC Block |

| Interrupt 1 1          | Analog Column 1           | PSoC Block |

| Interrupt12            | Analog Column 2           | PSoC Block |

| Interrupt13            | Analog Column 3           | PSoC Block |

| Interrupt14            | GPIO                      | Fixed      |

| Interrupt15            | Sleep Timer               | Fixed      |

Fig. 13.8

FIG. 14